Product Summary

The MT49H8M36FM-33 is a reduced latency DRAM (RLDRAM) II. The MT49H8M36FM-33 is a high-speed memory device designed for high bandwidth data storage-elecommunications, networking, and cache applications, etc. The MT49H8M36FM-33’s 8-bank architecture is optimized for sustainable high speed operation. The DDR I/O interface transfers two data words per clock cycle at the I/O balls. Output data is referenced to the free-running output data clock. Commands, addresses, and control signals are registered at every positive edge of the differential input clock, while input data is registered at both positive and negative edges of the input data clock(s). Read and write accesses to the RLDRAM are burst-oriented. The burst length (BL) is programmable from 2, 4, or 8 by setting the mode register.

Parametrics

MT49H8M36FM-33 absolute maximum ratings: (1)I/O voltage: -0.3 VDDQ + 0.3 V; (2)Voltage on VEXT supply relative to VSS: -0.3 +2.8V; (3)Voltage on VDD supply relative to VSS: -0.3 +2.1 V; (4)Voltage on VDDQ supply relative to VSS: -0.3 +2.1 V.

Features

MT49H8M36FM-33 features: (1)400 MHz DDR operation (800 Mb/s/pin data rate); (2)28.8 Gb/s peak bandwidth (x36 at 400 MHz clock frequency); (3)Organization, 32 Meg x 9, 16 Meg x 18, and 8 Meg x 36; (4)8 internal banks for concurrent operation and maximum bandwidth; (5)Reduced cycle time (20ns at 400 MHz); (6)Nonmultiplexed addresses (address multiplexing option available); (7)SRAM-type interface; (8)Programmable READ latency (RL), row cycle time, and burst sequence length; (9)Balanced READ and WRITE latencies in order to optimize data bus utilization; (10)Data mask for WRITE commands; (11)Differential input clocks (CK, CK#); (12)Differential input data clocks (DKx, DKx#); (13)On-die DLL generates CK edge-aligned data and output data clock signals; (14)Data valid signal (QVLD); (15)32ms refresh (8K refresh for each bank; 64K refresh command must be issued in total each 32ms); (16)144-ball μBGA package; (17)HSTL I/O (1.5V or 1.8V nominal); (18)25-60Ω matched impedance outputs; (19)2.5V VEXT, 1.8V VDD, 1.5V or 1.8V VDDQ I/O; (20)On-die termination (ODT) RTT.

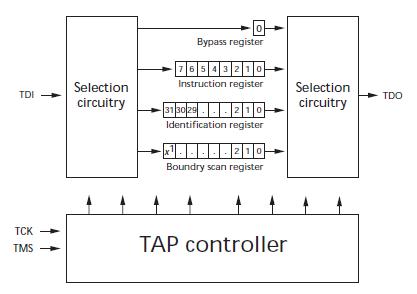

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

MT49H8M36FM-33 TR |

|

IC RLDRAM 288MBIT 300MHZ 144FBGA |

Data Sheet |

Negotiable |

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

MT49H16M16 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

MT49H16M16FM-5 TR |

|

IC RLDRAM 256MBIT 200MHZ 144FBGA |

Data Sheet |

Negotiable |

|

||||||

|

MT49H16M18 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

MT49H16M18BM-25:B |

|

IC RLDRAM 288MB 144UBGA |

Data Sheet |

|

|

||||||

|

MT49H16M18C |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

MT49H16M18CFM-5 IT |

|

IC RLDRAM 288MBIT 200MHZ 144FBGA |

Data Sheet |

Negotiable |

|

||||||

(China (Mainland))

(China (Mainland))